Layout of CMOS Inverter

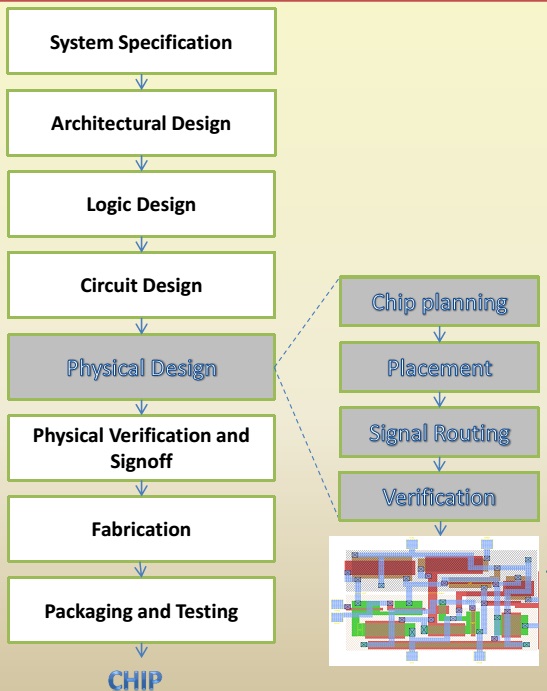

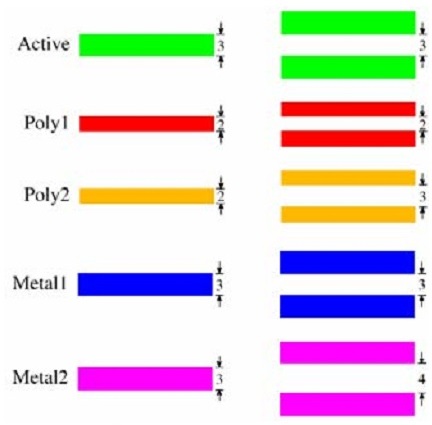

Layout is the process of drawing different mask layers of an IC. Each layer is drawn using a specific color and follows a set of design rules that act as an interface between the designer and the process engineer. Typical considerations include spacing, minimum width, overlap, manufacturability, performance, IC size, and parasitic elements.

Design Rules

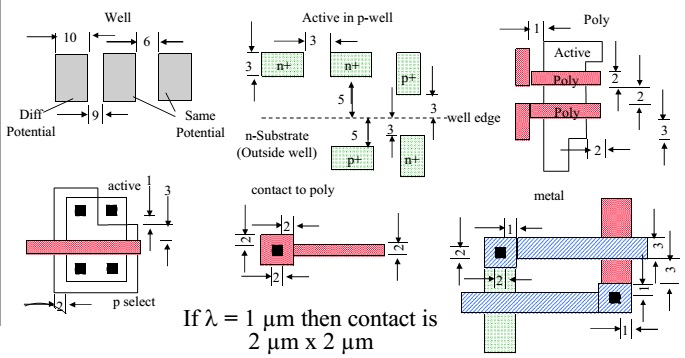

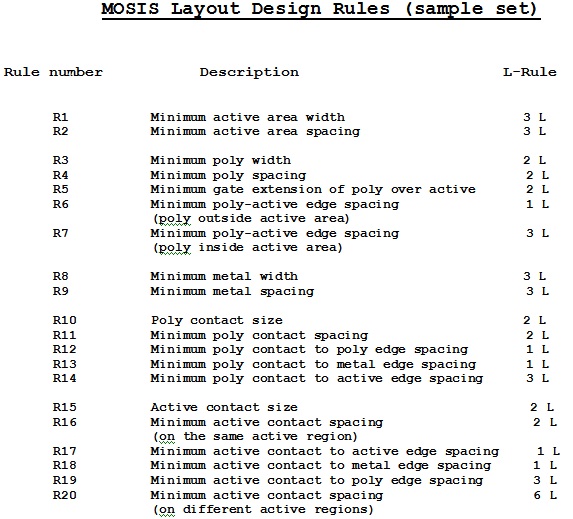

Design rules are categorized as Lambda (λ) rules and Micron rules:

1. Lambda-based rules

- Scalable rules based on a constant parameter (λ).

- 2λ equals minimum channel length; allows process portability.

- Processes rarely shrink uniformly, so adjustments may be needed.

2. Micron-based rules

- Minimum sizes and spacing specified directly in microns.

- Not tied to λ multiples; can reduce area by ~50% compared to λ rules.

Types of design rules include:

- Intra-layer: Width, spacing

- Inter-layer: Enclosures, distances, overlaps

- Specific rules: Antenna, density, minimum area

The λ rules were introduced by Mead and Conway (1980) to allow scalable, portable designs. The MOSIS service provides standard λ-rule sets for academic and commercial designs.

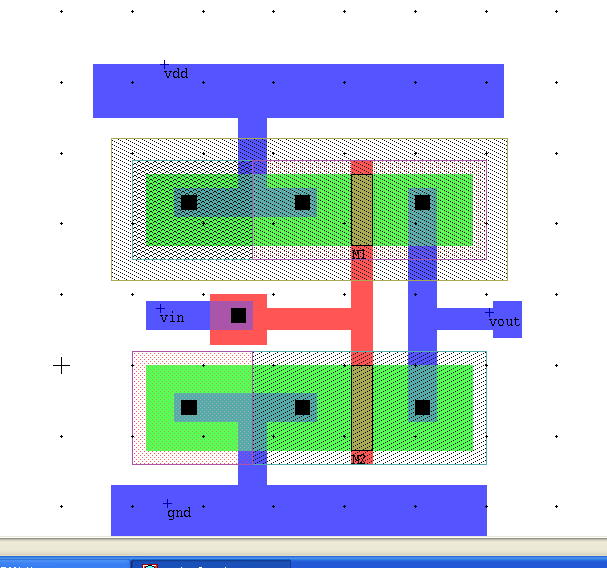

CMOS Inverter Layout

The layout is drawn in L-Edit following λ rules and CMOS process layers. After layout generation, it must pass:

- Design Rule Check (DRC): Automatically verifies that layout polygons follow all design rules.

- Layout versus Schematic (LVS) check: Ensures the layout matches the original circuit schematic.

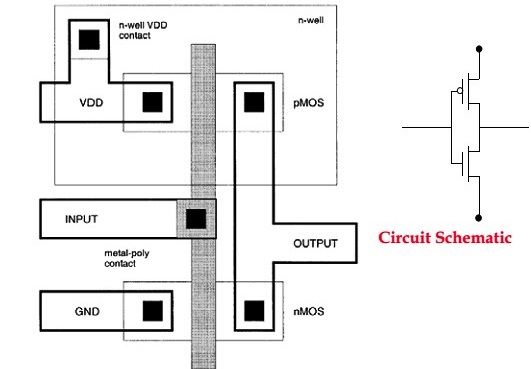

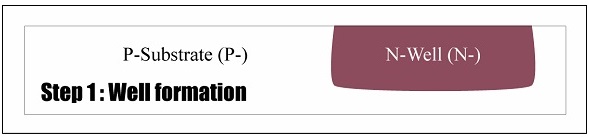

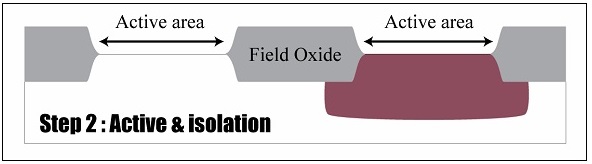

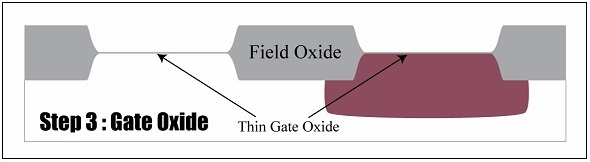

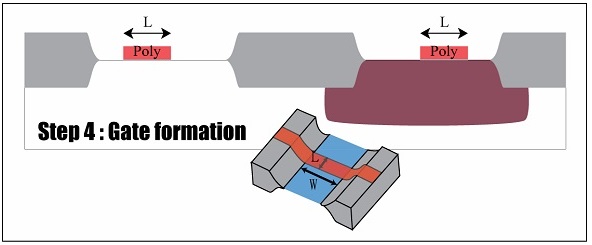

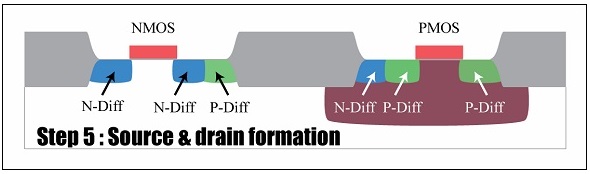

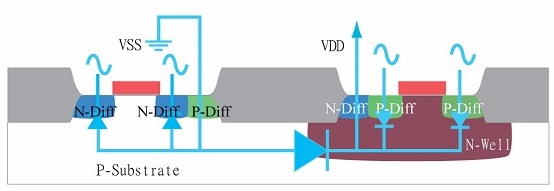

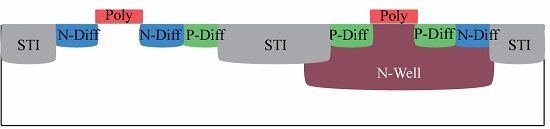

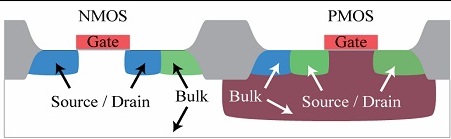

Cross-Sectional View

L-Edit allows visualizing the cross-section of the CMOS device, showing the fabrication steps. Observe the drains, sources, gates, and bulks of NMOS and PMOS transistors:

Key observations:

- Drain and Source are fabricated similarly.

- All NMOS bulks are connected together.

- All PMOS bulks in the same N-well are connected together.

SPICE Programming and Graphs

SPICE code can be extracted using T-Edit, and simulations with W-Edit produce the corresponding graphs for verification.

Conclusion

The CMOS Inverter layout drawn using L-Edit was successfully verified using DRC, LVS, and SPICE simulations. The process demonstrated proper adherence to design rules and layout correctness.